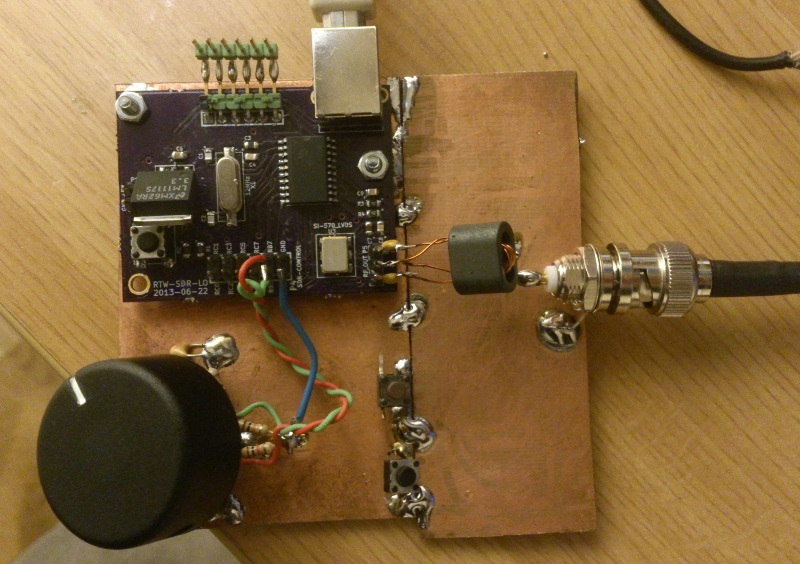

Si570 chip is a DSPLL PLL clock generator that is manufactured by Silicon Labs in several versions. The Si-570 chip version that I use on my RTW-SDR-LOCALOSCILLATOR BOARD has LVDS output. The chip supply voltage is 3.3 V. Si-570 has two output pins labeled as CLK+ and CLK-. This pins provide a differential output signal at the programmed frequency. Frequency range is 10-280 MHz. People have checked that the chip can go down to 10 MHz with no problems.

I had in my junk box a BN-43-302 binocular core from Micrometals. Also had a BN-43-2402 core but appeared to be very small for a trifilar winding. Having in mind that the transformer should have enough reactance to work at 3.5 MHz, I choosed the lowest number of turns that generated a reactance of at least 4 times the system impedance. I needed the required number of turns to have a reactance of at least 200 ohms. We have an useful WEB toroid calculator at http://toroids.info/BN-43-302.php

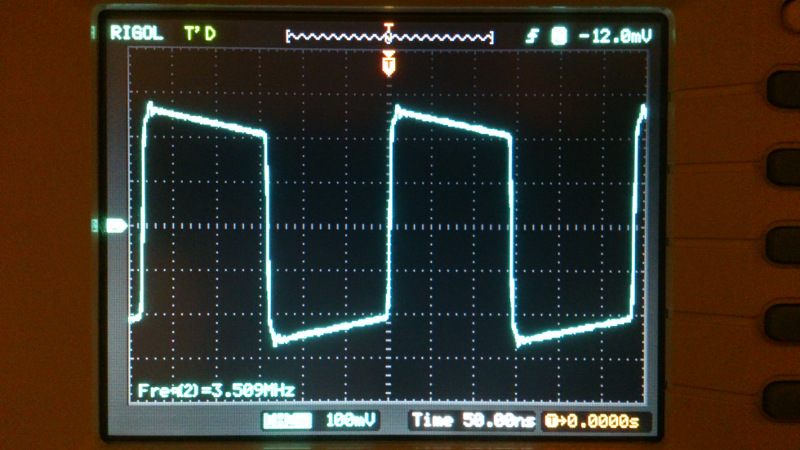

The core has an AL=1.28 uH per square turn. Three turns on the core has an inductance of 3^2*1.280 = 11.52 uH

At 3.5 MHz, the reactance is X = 2*pi*3.5e6*11.52e-6 = 253.34 ohms.

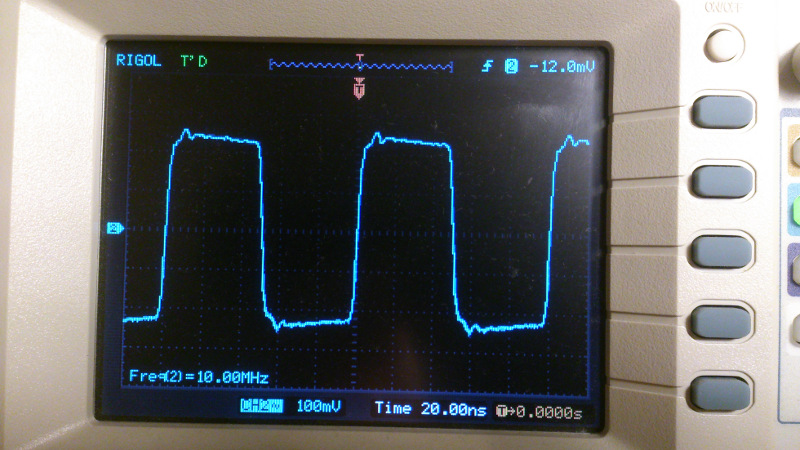

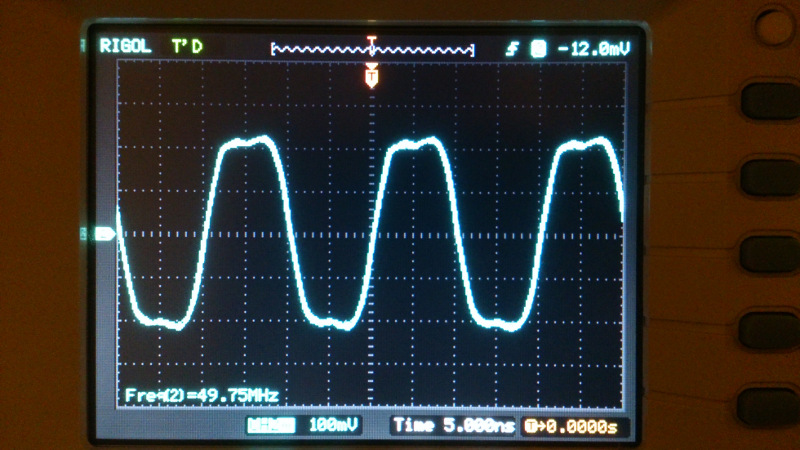

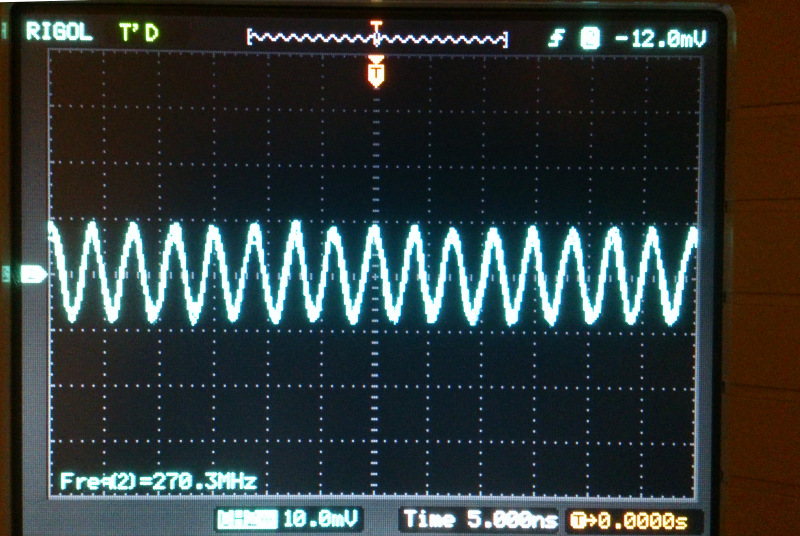

My oscilloscope has a 50 MHz bandwidth. The 100 MHz signal has a false sinusoidal appearance due to the limited bandwidth. I can see the signal at the maximum 280 MHz frequency but strongly attenuated, as you see in the oscilloscope screenshots.

Copyright (c) 2013 Ramiro Aceves . Permission is granted to copy, distribute and/or modify this document under the terms of the GNU Free Documentation License, Version 1.2 or any later version published by the Free Software Foundation; with no Invariant Sections, no Front-Cover Texts, and no Back-Cover Texts. A copy of the license is included in the section entitled "GNU Free Documentation License".